# Double-gate MOSFET Model Implemented in Verilog-AMS Language for the Transient Simulation and the Configuration of Ultra Low-power Analog Circuits

Billel Smaani, Yacin Meraihi, Fares Nafa, Mohamed Salah Benlatreche, Hamza Akroum, and Saida Latreche

Abstract—This paper deals with the implementation of a DC and AC double-gate MOSFET compact model in the Verilog-AMS language for the transient simulation and the configuration of ultra low-power analog circuits. The Verilog-AMS description of the proposed model is inserted in SMASH circuit simulator for the transient simulation and the configuration of the Colpitts oscillator, the common-source amplifier, and the inverter. The proposed model has the advantages of being simple and compact. It was validated using TCAD simulation results of the same transistor realized with Silvaco Software.

Keywords—double-gate MOSFET, compact model, ultra low-power analog circuits

#### I. Introduction

THE multiple-gates (MG) field-effect transistors (FETs) are promising devices for the scaling of the bulk metal-oxide-semiconductor (MOS) FETs, especially for their immunity to short-channel effects (SCEs) [1-3]. The MG FETs are Silicon on insulator (SOI) MOSFET with several gates, such as the double-gate MOSFET, the triple-gate MOSFET, and the surrounding-gate MOSFET [4].

However, the double-gate (DG) MOSFET remain one of the best MG FETs architecture in terms of electrical performances and the simple process of fabrication. Therefore, the DG MOSFET is a very promising device for VLSI technology [5].

On the other hand, compacts MGs FETs models coupled with circuit simulators are powerful tools for the design of analog and digital circuits with recent technology nodes [6], [7]. Moreover, the AC and DC behavior of the MGs FETs are well described with analytical compacts models, which include small geometry effects, leakage current, and quantum confinement effects. In this case, the simplicity and the accuracy are significant parameters for the use of this type of models in the design and the simulation of analog and mixed circuits [8].

Billel Smaani is with Ingénierie des Systémes Electriques Department, Faculty of Technology, Boumerdes University, Algeria (e-mail: b.smaani@univ-boumerdes.dz).

Yacin Meraihi and Fares Nafa are with Laboratoire d'Ingénierie et Systèmes de Télécommunications, Faculté de Technologie, Boumerdes (e-mail: y.meraihi@univ-boumerdes.dz, f.nafa@univ-boumerdes.dz).

Mohamed Salah Benlatreche is with Centre Universitaire Abdel Hafid Boussouf Mila, Algeria (e-mail: msbenlatreche@univ-boumerdes.dz).

Hamza Akroum is with Laboratoire d'Automatique Appliquée, Université M'Hamed Bougara de Boumerdes, Algeria (e-mail: akroum@gmail.com).

Saida Latreche is with Laboratoire Hyperfréquences et Semiconducteurs, Electronique Department, Constantine 1 University, Algeria (e-mail: latreche.saida@gmail.com).

In recent years, different compact models have been developed for MGs FET [9-11]. Just a few works have been carried out for the implementation of DG MOSFET compact models in the Verilog-A language [12-14], and most of the proposed works are dedicated to DC or AC models.

In this work, we have implemented a DC and AC double-gate MOSFET compact model in the Verilog-AMS language using SMASH circuit simulator for the transient simulation and the configuration of ultra low-power analog circuits, such as the Colpitts oscillator, the common-source amplifier, and the inverter. The proposed DC and AC model of the DG MOSFET is accurate, simple and compact.

Moreover, the Verilog-AMS language makes both Verilog-A and Verilog-HDL into the same MS-HDL language. Therefore, the Verilog-AMS offers a single language for the design of various circuits and systems with both analog and digital parts [15].

The paper is organized as follows. Section II presents the structure of the considered DG MOSFET transistor. Section III exposes the AC and DC model of the DG MOSFET transistor. Section IV gives the considered analog circuits: the Colpitts oscillator, the common-source amplifier, and the inverter. Section V presents the obtained results of the proposed model and circuits based on DG MOSFET. The last section concludes the paper and suggests some perspectives for future works.

## II. STRUCTURE OF DG MOSFET TRANSISTOR

We consider an n-type symmetrical double-gate MOSFET transistor.

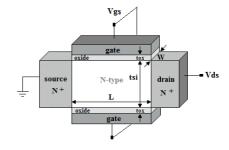

Indeed, Fig.1 illustrates the schematic view of the considered DG MOSFET transistor with the geometrical and technological parameters. Where L is the channel Silicon length, W(=L) is the channel silicon width,  $t_{ox}$  is the oxide thickness, and  $t_{si}$  is the Silicon thickness.  $V_{gs}$  and  $V_{ds}$  are the gate bias and the drain bias, respectively.

Fig. 1. Schematic diagram of the DG MOSFET transistor  $\,$

### III. MODEL DESCRIPTION

In the case of long channel n-type DG MOSFET and using the gradual channel approximation (GCA), the Poisson's equation can be written as [16], [17]:

$$\frac{d^2\Phi(y)}{dy^2} = \frac{q \cdot n_i}{\varepsilon_{si}} \exp\left(\frac{\Phi(y) - V_{ch}}{\Phi_t}\right)$$

(1)

where  $\Phi(y)$  is the electrostatic potential, q is the elementary charge,  $\varepsilon_{si}$  is the permittivity of silicon,  $n_i$  is the intrinsic carrier density,  $\Phi_t$  is the thermal voltage, and  $V_{ch}$  is the quasi-Fermi potential in the channel.

Applying the Gauss law at the interface of the Silicon and the gate oxide, after a second integration of (1), we obtain the following expression [18], [19]:

$$V_{gs} - V_{ch} = -\frac{Q_m}{2.C_{ox}}$$

$$+\Phi_t \cdot \ln \left( -\frac{Q_m^2}{8.\varepsilon_{si}.q.n_i.\Phi_t} - \frac{Q_m}{q.n_i.t_{si}} \right)$$

(2)

where  $Q_m$  is the mobile charge density per unit surface,  $C_{ox}$  is the oxide capacitance. It should be noticed that the mobile charge density can be computed iteratively from (2).

The drain-current model is obtained considering the drift-diffusion transport model through the integration of the mobile charge density in the channel (from Source to Drain) [1], [5]:

$$I_{ds} = -\mu \times \frac{W}{L} \int_{0}^{Vds} Q_{m} \, dV_{ch} \tag{3}$$

where  $\mu$  is low-field mobility.

Based on (3) and using (2), the expression of the draincurrent for the DG MOSFET transistor can be presented as follows:

$$I_{ds} = \mu..\Phi_{t} \times \frac{1}{2} \cdot \frac{W}{L} \times \left\{ Q_{m} \left( 1 + \frac{Q_{m}}{2.\Phi_{t}.C_{ox}} \right) + \frac{1}{2} C_{Si}.\Phi_{t}.\ln \left( 1 - \frac{Q_{m}}{8.\Phi_{t}.C_{Si}} \right) \right\}_{Oms}^{Qmd}$$

$$(4)$$

where  $C_{si}$  is the Silicon capacitance.

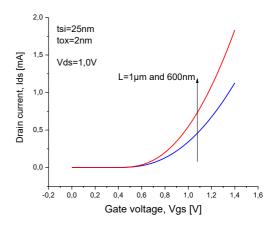

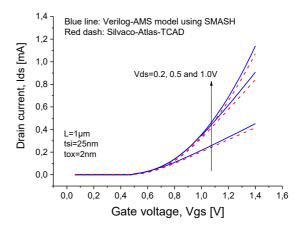

As result, Fig. 2 shows the variation of the modeled draincurrent  $I_{ds}$  against the gate bias  $V_{gs}$  for two different values of the channel length (L=1  $\mu$ m and 600nm).

As expected, we can note (from Fig. 2) that the current  $I_{ds}$  increase when the parameter L is decreased.

Fig. 2. Variation of the modeled drain-current  $I_{ds}$  versus the gate bias  $V_{gs}$ , for two various values of the parameter L

We define the capacitances of the DG MOSFET transistor as the derivative of the charges with respect to the terminals (gates, source, and drain), as follows [8], [20]:

$$C_{xy} = -\frac{\partial Q_x}{\partial Vy}\bigg|_{\substack{x \neq y \\ y \neq y}} = \frac{\partial Q_x}{\partial Vy}\bigg|_{\substack{x = y \\ y = y}}$$

(5)

where x, y stand for g, s and d (gate, source, and drain, respectively).

Using (5) and based on the EKV model for the MOSFET bulk [21], the gate to drain capacitance  $C_{dg}$  is given by:

$$C_{dg} = -1/15C_{ox\_r} \times \left\{ \left( 4\chi_f^3 + 6\chi_r^3 + 28\chi_f^2 \chi_r - 10\chi_f^2 \right) -15\chi_f \chi_r + 22\chi_f \chi_r^2 - 10\chi_r^2 \right) / \left( \chi_f + \chi_r \right)^3 \right\}$$

(6)

where  $C_{dg}$  is the gate to drain capacitance,  $C_{ox\_T} (= 2WLC_{ox})$  is the total oxide capacitance,  $\chi_f = \sqrt{1/4 + q_{0s}^2 - q_{0s}}$  and  $\chi_r = \sqrt{1/4 + q_{0d}^2 - q_{0d}}$ . With  $q_{0s}$  is the normalized charge in the source side and  $q_{0d}$  the normalized charge in the drain side

Similarly, the gate to source capacitance  $C_{Sg}$  is given by:

$$C_{sg} = 1/15.C_{ox\_T} \times \left\{ \left( 4\chi_r^3 + 6\chi_f^3 + 28\chi_r^2 \chi_f - 10\chi_r^2 \right) - 15\chi_f \chi_r + 22.\chi_r \chi_f^2 - 10\chi_f^2 \right\}$$

(7)

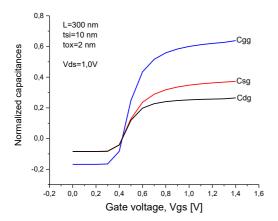

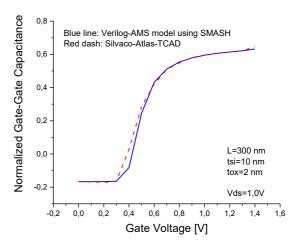

As shown in Fig. 3, we can see the variation of the normalized gate-to-gate capacitance  $C_{gg}$  (= $C_{sg}$ - $C_{dg}$ ), gate to source capacitance  $C_{sg}$  and gate to drain capacitance  $C_{dg}$  against the gate bias  $V_{gs}$ .

Fig. 3. Variation of the normalized main capacitances ( $C_{\rm gg}$ ,  $C_{\rm sg}$ , and  $C_{\rm dg}$ ) versus the gate bias  $V_{\rm gs}$ .

Additionally, the source to drain capacitance  $C_{ds}$  is given by:

$$C_{ds} = 2/15.C_{ox_{T}} \times \left\{ \left( (2\chi_{f} - 1) + (\chi_{f}^{2} + \chi_{r}^{2} + 3\chi_{f}\chi_{r}) \right) / (\chi_{f} + \chi_{r})^{3} \right\}$$

(8)

Also, the explicit expression of the drain to source capacitance  $C_{sd}$  is given by:

$$C_{sd} = -2/15.C_{ox_{T}} \times \left\{ \left( (2\chi_{r} - 1) + (\chi_{f}^{2} + \chi_{r}^{2} + 3\chi_{f}\chi_{r}) \right) / \left( \chi_{f} + \chi_{r} \right)^{3} \right\}$$

(9)

It is worth noticing that the capacitances  $C_{gs}$ ,  $C_{dd}$ ,  $C_{ss}$ , and  $C_{gd}$  are directly calculated using the other capacitances (6), (7) (8), and (9). With  $C_{gs}$  is the source to gate capacitance,  $C_{dd}$  is the drain to drain capacitance,  $C_{ss}$  is the source to source capacitance and  $C_{gd}$  is the drain to gate capacitance.

## IV. CONSIDERED ANALOG CIRCUITS

Based on the DG MOSFET transistor, we have considered different types of low power analog circuits: the Colpitts oscillator, the common-source amplifier, and the inverter.

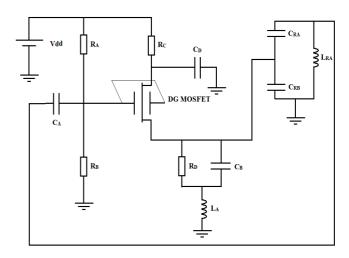

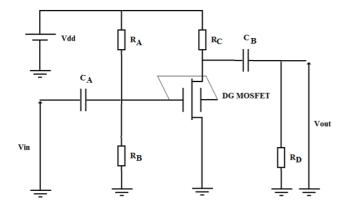

Fig.4, illustrates the circuit diagram of the DG MOSFET Colpitts oscillator [22-24].

To get a stable oscillation, the system in Fig.4 must satisfy the Barkhausen criteria:

$$\beta(w_0).G(w_0) = 1 \tag{10}$$

Where  $G(w_0)$  is the gain of the amplifier (DG MOSFET) and  $\beta(w_0)$  is the attenuation introduced by the tank (LC).

Fig. 4. Schematic view of the DG MOSFET Colpitts oscillator.

Then, the oscillation frequency is determined by the LC tank as:

$$w_0 = 1/\sqrt{L.C_{eq}} \tag{11}$$

with  $C_{eq} = C_{RA}.C_{RB}/(C_{RA} + C_{RB})$ .

Table I indicates the electrical parameters of the DG MOSFET Colpitts oscillator. The values of the components were selected to assume an operating point in the linear region and also to get a stable oscillation.

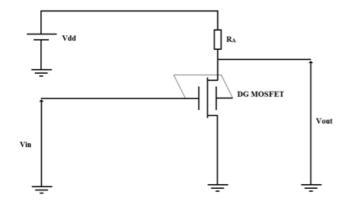

Fig.5 and Fig.6 show the circuit diagram of the DG MOSFET common-source amplifier and the circuit diagram of the DG MOSFET inverter, respectively. In both cases, the active and passive electronic devices were selected for the good behavior of the considered circuits. Also, for the amplifier circuit, the electronic components were selected to have an operating point in the linear region and to assume an appreciable amplification.

Table II shows the electrical parameters of the DG MOSFET common-source amplifier.

TABLE I

PARAMETERS OF THE DG MOSFET COLPITTS OSCILLATOR

| Parameters             | Symbol           | Value |

|------------------------|------------------|-------|

| Resistances $(\Omega)$ | $R_A$            | 75K   |

|                        | $R_{\mathrm{B}}$ | 120K  |

|                        | $R_{\mathrm{C}}$ | 50    |

|                        | $R_D$            | 50    |

| Capacitances (F)       | $C_A$            | 5n    |

|                        | $C_B$            | 10n   |

|                        | $C_D$            | 10n   |

|                        | $C_{RA}$         | 3p    |

|                        | $C_{RB}$         | 2p    |

| Inductances (H)        | $L_A$            | 30n   |

|                        | $L_{RA}$         | 1μ    |

Fig. 5. Schematic view of the DG MOSFET common-source amplifier

$\label{table II} \textbf{TABLE II}$  parameters of the DG MOSFET common-source amplifier

| Parameters               | Symbol           | Value |

|--------------------------|------------------|-------|

| Resistances ( $\Omega$ ) | $R_A$            | 100K  |

|                          | $R_{\mathrm{B}}$ | 100K  |

|                          | $R_{\mathrm{C}}$ | 250   |

|                          | $R_D$            | 200   |

| Capacitances (F)         | $L_{A}$          | 10μ   |

|                          | $L_{RA}$         | 10μ   |

Fig. 6. Schematic view of the DG MOSFET inverter

### V. RESULTS AND DISCUSSIONS

All of the considered analog circuits shown in Figs.4, 5, and 6 are based on the DG MOSFET transistor (Fig.1). The DC and AC behavior of this transistor are described using the analytical compact model detailed in section III. Then, the model is implemented in Verilog-AMS language using the SMASH circuit simulator [25].

Fig.7 presents the variation of the drain-current  $I_{ds}$  against the gate bias  $V_{gs}$  for different values of the drain bias  $V_{ds}(0.2, 0.5)$  and 1V). In this case, the results of the model in the Verilog-AMS are compared with the numerical simulation results of the DG MOSEFT obtained with the Silvaco-TCAD [26]. We can note the good agreement in all operation regimes between both the TCAD simulation (dash) and the model implemented in Verilog-AMS language (line).

Fig. 7. Comparison of the  $I_{ds}(V_{gs})$  characteristics using Verilog-AMS with Atlas-TCAD simulations, for various values of  $V_{ds}$ .

Fig.8 illustrates the computed gate-to-gate capacitance  $C_{gg}$  using the model in Verilog-AMS compared with the TCAD simulation results. As expected, the model using Verilog-AMS (line) shows a good agreement with the TCAD simulation results (dash).

Fig. 8. Comparison of the  $C_{gg}(V_{gs})$  characteristics using Verilog-AMS with Atlas-TCAD simulations

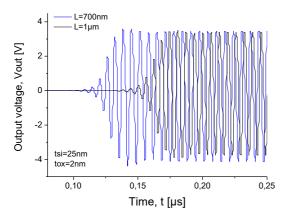

Fig.9 shows the variation of the output voltage for the DG MOSFET Colpitts oscillator obtained with the DG MOSFET model using Verilog-AMS and SMASH circuit simulator. The considered parameters of DG MOSFET are 25nm of the Silicon thickness,  $1\mu m$  and 700nm of the channel length, and 2nm of the oxide thickness.

We can see in Fig.9 the stability of the generated oscillation and especially the dependence of the time delay with the reduction of the device channel length L. Therefore, we have found that reducing the device channel length L creates an important variation in the amount of the inversion charge and the current  $I_{ds}$ , which allows for a slower time delay. Moreover, reducing the DG MOSFET parameters reduces the oscillator circuit size and makes the DG MOSFET an excellent candidate for RF (Radio Frequency) oscillator circuits. Also, the frequency oscillation is almost equal to 0.17 GHz.

Fig. 9. The output voltage of the DG MOSFET Colpitts oscillator obtained using Verilog-AMS and SMASH circuit simulator, for various values of L

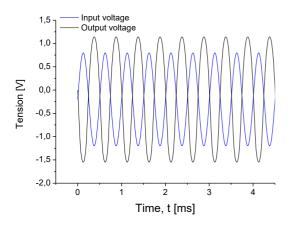

Fig.10 shows the result of the transient simulation for the DG MOSFET common-source amplifier, obtained using the DG MOSFET model implemented in Verilog-AMS with SMASH. The efficacy of the amplifier can be observed through the input signal (blue line) and the output signal (black line).

Fig. 10.Transient response of the DG MOSFET common-source amplifier obtained using Verilog-AMS and SMASH circuit simulator, with L=1 $\mu$ m,  $t_{si}$ =25nm, and  $t_{ox}$ =2nm

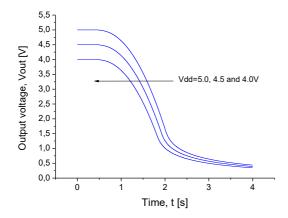

Fig.11.Transient response of the DG MOSFET inverter obtained using Verilog-AMS and SMASH circuit simulator, for various values of  $V_{\rm dd}$

Fig.11 shows the result of the transient simulation for the DG MOSFET inverter, obtained using the DG MOSFET model implemented in Verilog-AMS with SMASH. For different values of the voltage  $V_{dd}$  (4, 4.5, and 5V) the inverter has a good transient answer and excellent behavior.

## CONCLUSION

We have implemented a DC and AC DG MOSFET model in Verilog-AMS language targeting the transient simulation and the configuration of ultra low-power analog circuits. A physics-based compact model was established to describe DC and AC electrical behavior of the DG MOSFET and lowpower analog circuits using Verilog-AMS and SMASH circuit simulators. A good agreement was observed between the results of the compact model using Verilog-AMS and TCAD simulation results. We have considered different types of analog circuits based on the DG MOSFET model using Verilog-AMS: the Colpitts oscillator, the common-source amplifier, and the inverter. We have found in the case of the Colpitts oscillator that the dependence of the time delay with the device channel length is very important. As expected, a smaller delay is obtained with the reduction of the device parameters, especially the channel length. Also, the simulation and the configuration of the common-source amplifier and inverter prove the efficacy of the Verilog-AMS script for the model. In addition, the proposed DG MOSFET model using Verilog-AMS language presents excellent usefulness for the simulation, configuration, and design of various types of ultra low-power analog circuits.

#### REFERENCES

- [1] N. Arora, "MOSFET Modeling for VLSI Circuit Simulation: Theory and Practice," World Scientific, 1993.

- [2] International Technology Roadmap for Semiconductors. Available: http://www.itrs2.net, 2017.

- [3] O. Samy, H. Abdelhamid, Y. Ismail, A. Zekry, "A 2D compact model for lightly doped DGMOSFETs (P-DGFETs) including negative bias temperature instability (NBTI) and short channel effects (SCEs)," Microelectronics reliability, 2016, 67, 82-88.

- J-P. Colinge, "FinFETs and Other Multi-Gate Transistors," Springer, 2008

- [5] A. Amara, "Planar Double-Gate Transistor, From Technology to Circuit," Springer, 2009.

- [6] D. Stefanović, M. Kayal, M, "Structured Analog CMOS Design," Springer, 2008.

- [7] A. Mangla, M.-A. Chalkiadaki, F. Fadhuile, T. Taris, Y. Deval, C. C. Enz, "Design methodology for ultra low-power analog circuits using next generation BSIM6 MOSFET compact model," Microelectronics journal, 2013, 44, 570-575.

- [8] A.B. Bhattacharyya, "Compact MOSFET models for VLSI design," Wiley, 2009.

- [9] B. Smaani, S. Latreche, B. Iñiguez, "Compact drain-current model for undoped cylindrical surrounding-gate MOSFETs including short channel effects," J. Appl. Phys., 2013, 114.

- [10] J-M. Sallese, F. Krummenacher, F. Prégaldiny, "A design oriented charge-based current model for symmetric DG MOSFET and its correlation with the EKV formalism," Solid-State Electronics, 2012, 49, 485-489.

- [11] O. Moldovan, F. Lime, S. Barraud, B. Smaani, "Experimentally verified drain-current model for variable barrier transistor," IET Electronics Letters, 2015, 51, 17, 364–366.

- [12] J. Alvarado, B. Iñiguez, M. Estrada, "Implementation of the symmetric doped double-gate MOSFET model in Verilog-A for circuit simulation," Int. J. Numer. Model, 2010, 23, 88–106.

- [13] O. Cobianu, M. Soffke, A. Glesner, "Verilog-A model of an undoped symmetric dual-gate MOSFET," Int. Adv. Radio Sci, 2006, 4, 303–306.

- [14] M. Cheralathan, E. Contreras, J. Alvarado, "Implementation of nanoscale double-gate CMOS circuits using compact advanced transport models," Microelectronics Journal, 2013, 44, 80–85.

- [15] Verilog-AMS User Manual, Accellera 2006.

- [16] B. Smaani, M. Bella, S. Latreche, "Compact Modeling of Lightly Doped Nanoscale DG MOSFET Transistor," Applied Mechanics and Materials, 2014, 492, 06–10.

- [17] O. Samy, H. Abdelhamid, Y. Ismail, A. Zekry, "A 2D compact model for lightly doped DG MOSFETs (P-DGFETs) including negative bias temperature instability (NBTI) and short channel effects (SCEs)," Microelectronics Reliability, 2016, 67, 82-88.

- [18] Y. Taur, X. Liang, "A continuous, analytic drain-current model for DG MOSFETs," IEEE Electron device Letters, 2004, 25, 2, 107–109.

- [19] J-M. Sallese, A. S. Porret, "A novel approach to charge-based non-quasi-static model of the MOS transistor valid in all modes of operation," Solid-State Electronics, 2000, 44, 887-894.

- [20] H. Børli, S. Kolberg, "Capacitance modeling of short-channel double-gate MOSFETs," Solid-State Electronics, 2008, 52, 1486–1490.

- [21] C. Enz, F. Krummenacher, A.Vittoz, "An analytical MOS Transistor Model Valid in All Regions of Operation Dedicated to low voltage and low current applications," Analog and integrated Circuits and Signal Processing, 1995, 8, 83-114.

- [22] M. Bella, S. Latreche, C. Gontrand, "Nanoscale DGMOSFET: DC modification and Analysis of Noise in RF Oscillator," Journal of Applied Sciences, 2015, 5, 800–807.

- [23] R. Blaise, W. Tekam, J. Kengne, G. D. Kenmoe, "High frequency Colpitts' oscillator: A simple configuration for chaos generation," Chaos, Solitons & Fractals, 2019, 126, 351–360.

- [24] A.Rana1, P. Gaikwad, "Colpitts oscillator: design and performance optimization," Int. Journal of Applied Sciences and Engineering Research, 2014, 3, 913–919.

- [25] SMASH User Manual Version 5.18 Release, 2012.

- [26] Device simulator ATLAS, Silvaco International, 2007.